From the below picture we can see that. For PCBs far end crosstalk is usually negative current due to Lm larger than current due to Cm.

Team Vlsi Crosstalk Noise And Crosstalk Delay Effects Of Crosstalk

In VLSI we have same situation with the nets routed that even nets are at their track but impacted by the noise from other nets.

. Crosstalk VLSI Guide 0025 Signal Integrity 2 comments Definition Due to the influence of cross coupling capacitance switching of the signal from one net aggressor to the neighboring net victim. These are basically called as VIAs. This video covers the basics that you need to start with analysing crosstalk noise crosstalk delay reports in VLSI Digital IC Designs.

This is known as crosstalk. Crosstalk may lead to set up and hold violation. VLSI physical design interview questions and answers.

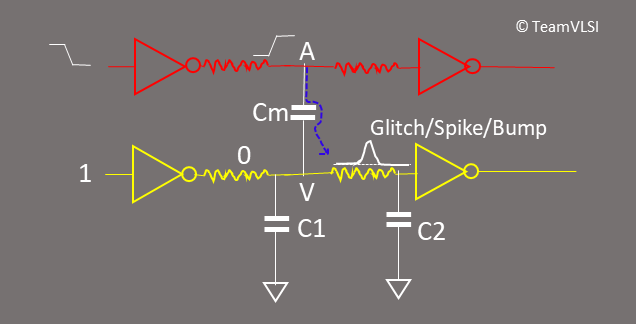

Refer to the digram below to get a clear picture on the effect of coupling capacitance on functionality and timing of VLSI circuits. Delays for setup calculation and min. If IR drop is more delay is increases.

And crosstalk in VLSIs IEEE Trans. There are several tools in existence which extract resis- tancecapacitance RC networks from layouts. The tool calculates max.

In the next section we would discuss the crosstalk mechanism in VLSI Design. Note that far end crosstalk can be positive. Same design constraints yet use less running time.

Delays for hold worst- and best-case analysis. 12 DECEMBER 1999 1817 Short Papers Crosstalk in VLSI Interconnections. Crosstalk Crosstalk is the undesirable electrical interaction between two or more adjacent nets due to capacitive cross-coupling.

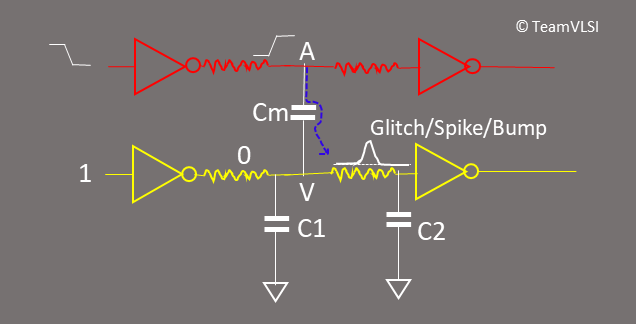

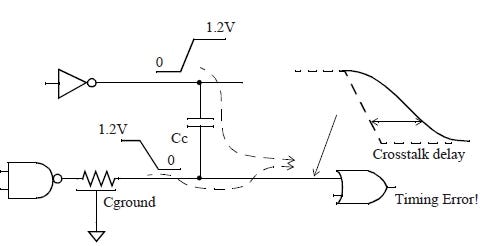

If we have crosstalk then we might lose data or gain some extra datalogic which was not required. Crosstalk is the result of mutual capacitance Cm in conjunction with mutual inductance Lm between adjacent conductors. The aggressor net has a rising transition at the same time when the victim net has a falling transitionThe aggressor net switching in the opposite direction increases the delay for the victim.

Aggressor is a net which creates impact on the other net. Crosstalk mechanism Crosstalk occurs via two mechanisms. INTRODUCTION Global routing plays an important role in veryultra large scale integrated circuit VLSIULSI physical design.

During the transition on adjacent signal aggressor net causes a noise bumpglitch on constant signal victim net. This unwanted element is called Signal Integrity. Crosstalk in VLSI interconnections.

These values are defined so that optimization and analysis can ensure that the spurious signals. Crosstalk induced noise Voltage profile of coupled noise Near end crosstalk is always positive currents from Lm and Cm always add and flow into the node. Crosstalk is a very severe effect especially in lower technology node and high-speed circuits and it could be one of the main reason of chip failure.

Refer to the diagram below to get a clear picture on the effect of coupling capacitance on functionality and timing of VLSI circuits. VIAs in VLSI. The work in 15 and 16 derives bounds for crosstalk Ashok Vittal.

Signal integrity and crosstalk are quality checks of the clock routes. As chip size decreases the standard cell density and routing density of the design increases due to that metal routes may interact with each other and it may result in a coupling effect which is known as crosstalk. When you perform crosstalk analysis using PrimeTime SI a change in delay due to crosstalk along the common segment of a clock path can be pessimistic but only for a zero-cycle check.

This video will give you a quick overview of various fixing methods that can be applied during eco implementation phase in ASIC physical design in VLSIFollo. 12 DECEMBER 1999 1817 Short Papers Crosstalk in VLSI Interconnections differential equations for a pair of lines to arrive at a crosstalk expression. Near-end-crosstalk Far-end-crosstalk 15.

For simplicity and for measuring the magnitude of noise induced on to the adjacent transmission lines we have to consider the two terms. Noise margin is the amount of noise a circuit can withstand without compromising its operation. Presented at the 1999 International Conference on VLSI Design 17.

Physical design interview questionsphysical design interview questions in vlsivlsi physical design interview questionsphysical design interview questions vlsi4fresherscadence interview questionsphysical design interview questions pdf. It affects both signal nets as well as clock nets. What are VIAs in VLSI.

And it also explains. To connect between different metal layers we need poly layer along with the metal layers that we are going to connect. Crosstalk is a phenomenon by which a logic transmitted in vlsi circuit or a netwire creates undesired effect on the neighbouring circuit or netswires due to capacitive coupling.

14 Crosstalk induced noise. Switching of the signal in one net aggressor can interfere neighbouring net victimdue to cross coupling capacitance this is called cross talk. Inductive Crosstalk Electrostatic crosstalk.

CRPR and Crosstalk Analysis. Lets consider a buffer that is placed in a common path both data path and clock path for buf2 and buf3 buffer. The positive crosstalk impacts the driving cell as well as the net interconnect - the delay for both gets increased because the charge required for the coupling capacitance Cc is.

Crosstalk is a phenomenon by which a logic transmitted in vlsi circuit or a netwire creates undesired effect on the neighboring circuit or netswires due to capacitive coupling. New challenges to global routing are coupling noise crosstalk elimination and performance optimizations 1. IEEE TRANSACTIONS ON COMPUTER-AIDED DESIGN OF INTEGRATED CIRCUITS AND SYSTEMS VOL.

Crosstalk in VLSI interconnections - Computer-Aided Design of Integrated Circuits and Systems IEEE Transactions on IEEE TRANSACTIONS ON COMPUTER-AIDED DESIGN OF INTEGRATED CIRCUITS AND SYSTEMS VOL. Physical design levels and finally ways to face these challenges early in a. Crosstalk is the unwanted coupling of energy between two or more adjacent lines which can change the required signal and is also termed as Xtalk Occurs on long adjacent wires Can be interpreted as the coupling of energy from 1 line to another via.

Crosstalk Analysis And Its Impact On Timing In 7nm Technology By Einfochips An Arrow Company Medium

Cts Part Ii Crosstalk And Useful Skew Vlsi Physical Design For Freshers

Mantra Vlsi Crosstalk Questions

Crosstalk Analysis And Its Impact On Timing In 7nm Technology By Einfochips An Arrow Company Medium

Crosstalk Analysis And Its Impact On Timing In 7nm Technology By Einfochips An Arrow Company Medium

Cts Part Ii Crosstalk And Useful Skew Vlsi Physical Design For Freshers

Optimization Of Crosstalk Delta Delay On Clock Nets

Team Vlsi Crosstalk Noise And Crosstalk Delay Effects Of Crosstalk

0 comments

Post a Comment